Welcome to cdstahl.org

Welcome to cdstahl.org. Here you will find a collection of my projects and short notes about a variety of electrical engineering subjects. Most articles are designed to be short and informative, but may require some background information.

Currently, I have categories for FPGA, Fundamentals, VHDL, and Math.

Some pages have code provided.

There are several people with the name C. D. Stahl. There is at least one other person who also has an electrical engineering background. If you reached this website as part of a background/experience check, please keep this in mind. I do list this website on my resume, when applicable.

Viterbi Decoder

A recent personal project was a Viterbi Decoder for a classic constraint length seven convolutional code. This type of error coding and decoding was an interesting challenge. The decoder design allows for some creative uses of the Virtex-6’s block RAMs. The decoder also is a nice design challenge because it is comprised of a large array of simple operations. This means some aspects need to be kept as simple as possible to avoid excessive resource usage. (Picture is actually of the encoder operation.)

ML605

Most of the FPGA related articles focus on my ML605 evaluation board from Xilinx. This board has a Virtex6 LX240T-1. This part is a very large FPGA, with 768 DSP48 slices, 416 block rams. The fabric is also fast and there’s a good deal of it (37,680 slices). The eval board is relatively affordable — on the upper end of “hobbyist.” When Post-PAR results are listed, it is for this part.

Reed-Solomon

One of my interests is in coding — not programing or scripting. I do a bit of programming and scripting as well, but in this case I’m referring to representing data in some encoded form. I had always had an interest is LFSRs, which are related to Galois Fields. It seemed like an interesting task to examine how algorithms using Galois Fields might be implemented on an FPGA.

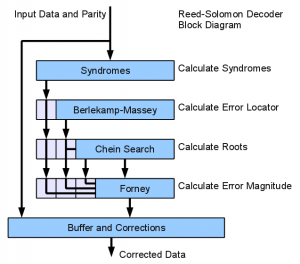

The Reed-Solomon encoder/decoder are natural choices to explore this task. The encoder is a fancy LFSR, similar to a CRC check, but a bit more complex. The decoder can be broken into several sub-algorithms, each with a slightly different challenge.

Sequences

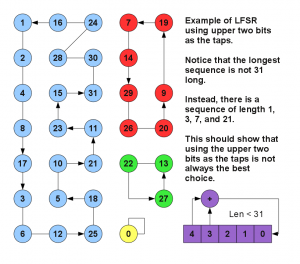

One of my interests is in LFSRs and NLFSRs. These are sequence generating circuits designed to be simple. I have many open questions about these. Nearly all of the literature on LFSRs is dedicated to the maximal length case. I often wonder about the non-maximal length case — what lengths are possible? The same for the nonlinear feedback case.

I also find Gray-Code and related topics to be interesting.

VHDL and Verilog

Most of my articles are targeted to VHDL. This is mainly because Xilinx hasn’t offered support for the higher level SystemVerilog features in ISE. Luckily the biggest complaint with VHDL– the verbosity — can be helped with a good editor or IDE. That said, I used Verilog for several years in college. Every once in a while, I write a quick Verilog project to keep up my skills.

Analog Design

I also have a considerable interest in analog design. I started with analog filter design, but also have made a range of RF and power circuits. Even with the advent of DSP and its wonderful ability to reduce the analog hardware requirements, analog is still a vital portion of most systems.