This is a short post. Tools like XST do support division by powers of two for numeric types in VHDL. However, VHDL defines division in a mathematically consistent way, which is not the same as C.

This is the issue — the above infers a round toward zero behavior. After all, rounds to

, so

should be the same as

. At the same time,

should be the same algebraically. However, in C programming,

would round down to

.

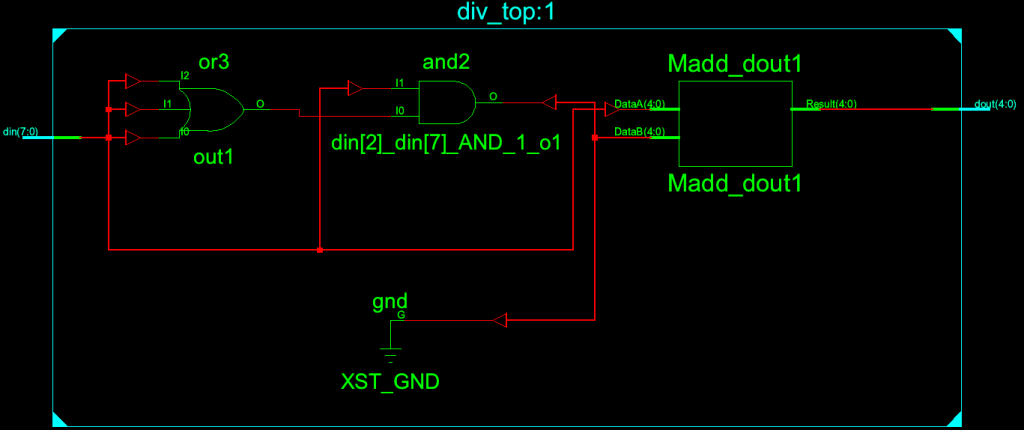

Notice that the schematic from a simple division by constant 8 infers some logic to perform the round toward zero that is implied by VHDL.

Many users will expect the C-style truncation, or round toward negative infinity, as this is a simple renaming of bits and infers no physical logic.